# Reduction of Crosstalk Between Dual Power Amplifiers Using Laser Treatment

Huan-Lin Chang, Student Member, IEEE, P.-S. Kuo, W.-C. Hua, Chun-Ping Lin, Che-Yung Lin, and C. W. Liu, Senior Member, IEEE

*Abstract*—A cost-effective isolation technique using laser treatment is proposed to suppress the undesired crosstalk between dual power amplifiers (PAs), which are essential to multiple-input multiple-output communications system. Laser treatment not only reduces the small-signal coupling between dual PAs but also enhances the linearity of the PA under dual-PA operation mode. The figure of merit for the small-signal coupling has an improvement of 4.55 dB at 2.45 GHz, and the output power at 3% (-30 dB) error vector magnitude (EVM) has a linearity improvement of 6.1 dB under 0-dB interference.

*Index Terms*—Coupling, crosstalk, isolation, laser treatment, multiple input multiple output (MIMO), power amplifiers (PAs).

# I. INTRODUCTION

T HE trend of wireless communications is moving toward the era of high data-throughput transmission. Various developed and developing wireless communications standards incorporate the multiple-input multiple-output (MIMO) technique to meet the demanding high-data-rate requirement. To achieve the goal, dual or multiple power amplifiers (PAs) are indispensable in MIMO radio frequency (RF) front-end circuits. However, several PAs operating at the same time inevitably pose crosstalk problems [1]. Compounding the problem is the adoption of the orthogonal frequency-division multiplexing (OFDM) modulation scheme because of the inherently high peak-to-average power ratio (PAPR). The PA needs a wide linear range to deal with the highly varying envelope of the signal.

As reported in [2], substrate coupling resulting from the low resistivity ( $\sim 10 \Omega$ . cm) of bulk Si substrate is the primary cause for the existence of crosstalk. A number of effective techniques have been proposed to suppress the undesired coupling by using the silicon-on-insulator (SOI) substrate [3], [6]–[8], high resistivity p-substrate [2]–[5], guard ring shielding [1], [3]–[7], and porous Si trench [9]. Most of the studies proceed from a device standpoint. At the circuit level, the deep trench and guard rings were used to reduce the coupling between PAs [1]. In this letter, the laser treatment (L.T.) is utilized in a more efficient fashion to reduce the crosstalk.

The authors are with the Department of Electrical Engineering and Graduate Institute of Electronics Engineering, National Taiwan University, Taipei 10617, Taiwan, R.O.C. (e-mail: chee@cc.ee.ntu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LMWC.2008.2002456

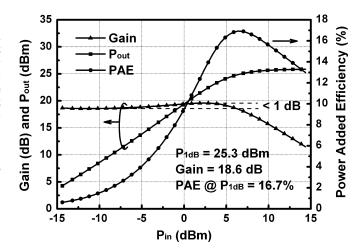

Fig. 1. Power performance of the single PA, where  $P_{1 dB}$  is 25.3 dBm, linear gain is 18.6 dB, and PAE at  $P_{1dB}$  is 16.7%. The gain expansion is shown to be less than 1 dB (dashed lines).

### **II. CIRCUIT PERFORMANCE EVALUATION**

## A. Single PA Performance

The dual PAs are fabricated with a symmetrical layout on the same chip using the TSMC SiGe BiCMOS process. The size of the die is 1680  $\mu$ m × 1680  $\mu$ m, and the distance between two power amplifiers is 150  $\mu$ m. The emitter width of the transistors in dual PAs is 0.9  $\mu$ m. Fig. 1 indicates the power performance of the single PA, where the 1-dB compression point of the output power (P<sub>1dB</sub>) is 25.3 dBm, linear power gain is 18.6 dB, and power-added efficiency (PAE) is 16.7%. The mismatch of power characteristics between dual PAs is negligible. The transistor sizes of the bias circuit are optimally selected to minimize the undesired gain expansion to less than 1 dB. However, the earned gain flatness is traded off by the efficiency degradation due to the increase of dc biasing current. The circuit schematic can be found in our previous work [1].

### B. Figure of Merit for Coupling

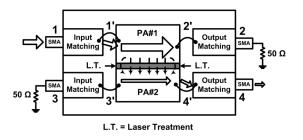

Fig. 2 shows the schematic of the printed-circuit board (PCB) layout. The first PA (PA#1) and the second PA (PA#2) are on the same die with bondwires connecting to the input- and output-matching networks. Offchip matching is used due to the flexibility in tuning the matching components.

A four-port S-parameter experiment is involved in the performance characterization of dual PAs. Ports 1 to 4 are the outer ports directly connected to the HP8753D network analyzer while port 1' to port 4' are the inner ports excluding the inputand output-matching networks. The inner ports are of interest

Manuscript received March 4, 2008; revised May 20, 2008. Current version published September 5, 2008. This work was supported by National Science Council, Taiwan, R.O.C., under Contracts 96-2221-E-002-251 and 96-2221-E-002-288.

Fig. 2. Schematic of the PCB layout and illustration of the coupling signal flow from port 1 to port 4 in the four-port *S*-parameter measurement.

for extracting the coupling signal. Fig. 2 shows one of the coupling signal flows from port 1 to port 4 by arrows, where the size of the arrows implies the amplification and attenuation of the traveling signal. The similar coupling signal flow from ports 3 to 2 also exists, but is not shown for clearness. Note that the input- and output-matching networks induce 2–3-dB signal loss in the signal traveling path.

To determine the amount of the crosstalk, the figure of merit for the small-signal coupling proposed in [1] is adopted. With the PA#1 and the PA#2 both turned on, the input signal from port 1 can be measured at output port 2 and output port 4, where the former is the desired amplified signal and the latter is the unwanted coupling signal. The equivalent coupling can be defined as

$$Seq = |S_{4'1'}| - |S'_{2'1}|$$

= (|S\_{41}| - |S\_{1'1}| - |S\_{44'}|)

- (|S\_{21}| - |S\_{1'1}| - |S\_{22'}|)

= |S\_{41}| - |S\_{21}| (1)

where  $|S_{44'}| = |S_{22'}|$  because of the symmetrical layout [1]. Note that  $|S_{41}|$  and  $|S_{21}|$  can be directly obtained by the network analyzer and, thus, the equivalent coupling  $S_{eq}$  is obtained in decibels. In the four-port measurement, the nonmeasured ports are matched with the 50- $\Omega$  load as shown in Fig. 2.

#### **III. ISOLATION TECHNIQUE AND EXPERIMENTAL RESULTS**

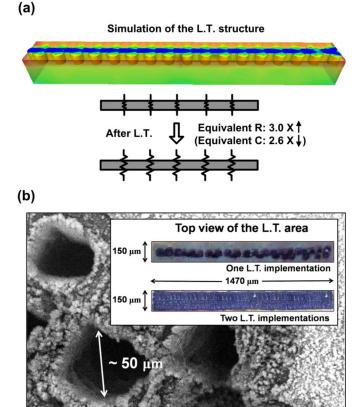

The L.T. area between two PAs is 1470  $\mu$ m  $\times$  150  $\mu$ m (Fig. 2). The L.T. is utilized to impair the smooth layer structure of the chip and induce scattered holes in the substrate. This structure causes the equivalent resistance of the L.T. area to be effectively higher, thus suppressing the coupling between dual PAs. The qualitative effect of the resistive coupling can be simulated by ISE TCAD software, and the result is shown as in Fig. 3(a). The simulation scenario is that there are three rows of L.T.-induced holes closely arranged in the silicon substrate with 10-nm hole spacing. The equivalent resistance of the L.T. area is three times larger than that without L.T. Also, the equivalent capacitance is 2.6 times lower than that without L.T. Fig. 3(b) shows the SEM image of the top-view L.T. area, and the inset shows the photographs of the entire area after one and two L.T. implementations. For one L.T. implementation, a series of laser shots is applied to the L.T. area, creating a row of scattered holes. The equivalent power density of one L.T. implementation is  $\sim 2.5 \,\mu W/\mu m^2$ . For two implementations, about twice as

Fig. 3. (a) Simulation of the L.T. structure with three rows of L.T.-induced holes (10-nm hole spacing). The equivalent resistance of the L.T. area is three times larger than that without L.T. (b) Top-view SEM image which demonstrates the impact of one L.T. implementation. The inset shows the photograph of the entire L.T. area (1470  $\mu$ m × 150  $\mu$ m) after one and two L.T. implementations.

many laser shots are applied to the previous L.T. area, making the overlap of scattered holes more uniform. The applied laser pulses are adjustable in power levels and spot sizes. In our experiment, laser pulses are applied in the burst mode at the intensity of 80  $\mu$ W/shot. The L.T.-induced holes are ~50  $\mu$ m in diameter and ~50  $\mu$ m in depth inside the ~150- $\mu$ m-thick die.

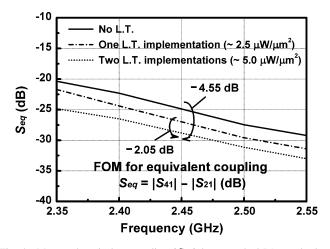

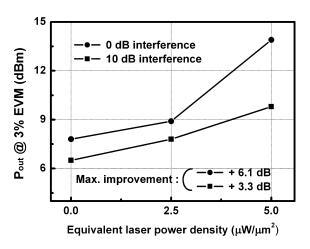

Fig. 4 shows the reduction of the equivalent coupling  $S_{eq}$  after L.T. implementation around the 2.45-GHz band. At the operating frequency (2.45 GHz) of the PAs, a 2.05-dB improvement is achieved after one L.T. implementation, and a 4.55-dB improvement is achieved after two L.T. implementations. Fig. 5 shows the L.T. effect on the large signal output-power performance. To judge the linearity of the PA under digitally modulated signal operation, error vector magnitude (EVM) can be readily measured rather than the tedious bit-error rate (BER) test.

To meet the wireless local-area network (WLAN) communications specification, EVM is required to be 3% (-30 dB) or less for a sufficiently linear PA. Thus, the output power at 3%EVM can serve as a good indicator to judge the linearity of the PA. The impact of different interference levels is also demonstrated in Fig. 5. For an MIMO system using a digital modulation scheme, such as OFDM, it is very likely that different power

Fig. 4. Measured equivalent coupling  $(S_{\rm eq})$  between dual PAs as the laser power density increases. The  $S_{\rm eq}$  shows a 4.55-dB reduction at 2.45 GHz after two L.T. implementations (power density  $\sim 5.0 \ \mu W/\mu m^2$ ).

Fig. 5. Measured  $\rm P_{out}$  at 3% EVM versus laser power density under different interference levels. The linearity shows a maximum 6.1-dB improvement under 0-dB interference.

levels are sent into each PA, which sees the other PA as an interference source. In Fig. 5, the definition of the 0-dB interference is that the main PA (PA#1) and the interfering PA (PA#2) are operating at the same power levels. Similarly, the 10-dB interference means that the interfering PA is operating at a power level 10 dB higher than the main PA.

The crosstalk signal from the interfering PA is resistively coupled to the main PA, and intermodulates with the main signal to yield AM–AM and AM–PM nonlinearities. These nonlinearities degrade EVM in the constellation plot. Thus, the reduction of crosstalk facilitates the EVM performance of the PA. The maximum linearity improvement after two L.T. implementations is 6.1 dB under 0-dB interference, and is 3.3 dB under 10-dB interference. Though larger interferences will worsen the linearity of the PA, the isolation between dual PAs still benefits from the L.T. technique even under 10-dB interference.

# IV. CONCLUSION

Laser treatment at different power densities effectively reduces the crosstalk between dual PAs. The cost-effective technique not only provides good isolation for small-signal coupling but also enhances the linearity of the PA under dual-PA operation mode. The figure of merit for equivalent coupling has a reduction of 4.55 dB after two L.T. implementations with a laser power density of ~5.0  $\mu$ W/ $\mu$ m<sup>2</sup>. Furthermore, the largesignal output-power performance shows a maximum linearity improvement of 6.1 dB under the 0-dB interference condition. A maximum linearity improvement of 3.3 dB is achieved even under the 10-dB interference condition. As far as the process compatibility is concerned, the L.T. technique serves as a good candidate for further integration into the back-end manufacturing.

#### ACKNOWLEDGMENT

The authors would like to thank the National Chip Implementation Center (CIC) for their assistance.

#### REFERENCES

- [1] W.-C. Hua, P.-T. Lin, C.-P. Lin, C.-Y. Lin, H.-L. Chang, C. W. Liu, T.-Y. Yang, and G.-K. Ma, "Coupling effects of dual SiGe power amplifiers for 802.11n MIMO applications," in *Proc. IEEE Radio Frequency Integrated Circuits Symp. Dig.*, Jun. 2006, pp. 81–84.

- [2] Y. H. Wu, A. Chin, K. H. Shih, C. C. Wu, C. P. Liao, S. C. Pai, and C. C. Chi, "Fabrication of very high resistivity Si with low loss and cross talk," *IEEE Electron Device Lett.*, vol. 21, no. 9, pp. 442–444, Sep. 2000.

- [3] M. Pfost, P. Brenner, T. Huttner, and A. Romanyuk, "An experimental study on substrate coupling in bipolar/BiCMOS technologies," *IEEE J. Solid-State Circuits*, vol. 39, no. 10, pp. 1755–1763, Oct. 2004.

- [4] D. Kosaka, M. Nagata, Y. Hiraoka, I. Imanishi, M. Maeda, Y. Murasaka, and A. Iwata, "Isolation strategy against substrate coupling in CMOS mixed-signal/RF circuits," in *Proc. IEEE VLSI Circuits Symp. Tech. Dig.*, Jun. 2005, pp. 276–279.

- [5] C. Barbier-Petot, S. Bardy, C. Biard, and P. Descamps, "Substrate isolation in 90 nm RF-CMOS technology," in *Proc. Eur. Microwave Conf.*, Oct. 2005, pp. 89–92.

- [6] J.-P. Raskin, A. Viviani, D. Flandre, and J.-P. Colinge, "Substrate crosstalk reduction using SOI technology," *IEEE Trans. Electron Devices*, vol. 44, no. 12, pp. 2252–2261, Dec. 1997.

- [7] M. Kumar, Y. Tan, and J. K. O. Sin, "Novel isolation structures for TFSOI technology," *IEEE Electron Device Lett.*, vol. 22, no. 9, pp. 435–437, Sep. 2001.

- [8] J. Ankarcrona, L. Vestling, K.-H. Eklund, and J. Olsson, "Low resistivity SOI for substrate crosstalk reduction," *IEEE Trans. Electron Devices*, vol. 52, no. 8, pp. 1920–1922, Aug. 2005.

- [9] H.-S. Kim, K. A. Jenkins, and Y.-H. Xie, "Effective crosstalk isolation through p+Si substrates with semi-insulating porous Si," *IEEE Electron Device Lett.*, vol. 23, no. 3, pp. 160–162, Mar. 2002.